石英晶體振蕩器按照類型可以分為多種類別,而差分晶振則是有源晶振中高級別的.差分晶振相較于普通晶振而言,低電流電壓可達到低值1V,工作電壓在2.5V-3.3V,是普通貼片晶振所不能夠達到的,差分晶振具有低電平,低抖動,低功耗等特性.差分晶振作為目前行業中要求高的,技術高的石英晶體振蕩器,具有相位低,損耗低的特點.差分貼片晶體振蕩器使用于產品中能夠很容易地識別小信號,能夠從容精確地處理'雙極'信號,對外部電磁干擾(EMI)是高度免疫的.

對于一個在這種電路設計的新手去設計一個ADC系統,通過AD9269將1MHz到10MHz的模擬信號數字化.第一次看到數據表中的"時鐘輸入考慮"部分時,是很困惑.根據理解,如果有一個低抖動時鐘源(例如石英晶體振蕩器),那么基于PLL的時鐘發生器/分配器(例如數據表和評估板設計中推薦的AD9517)可能不是首選.

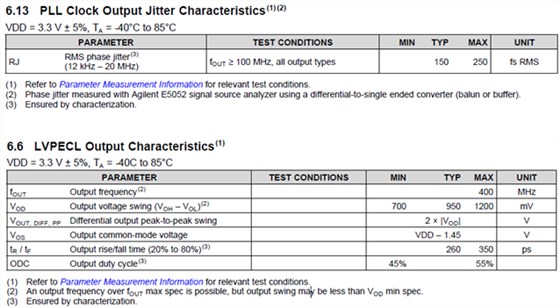

在設計中,將使用專用于AD9269的單個時鐘源.所以猜測,使用單個低抖動晶體振蕩器將是最佳選擇.主要考慮的是如何使用~10MHz模擬正弦輸入信號最大化ADC中的ENOB.如果有更合適的時鐘源設計,請推薦.假設有源晶振(XO)是最佳選擇,我發現一些XO(例如LMK60E2-156M)提供<200fsRMS抖動和LVPECL輸出(參見下表).

我決定使用這種XO,但是一旦我參考AD9269數據表來完成我的設計,我就會遇到一些問題:

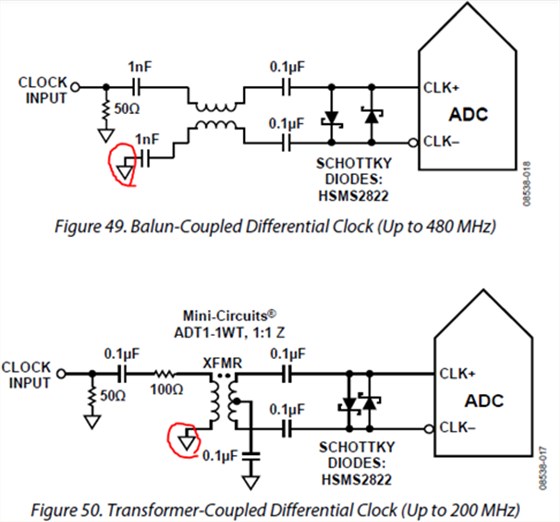

(1)如果XO提供LVPECL差分晶振輸出,我還需要ADCCLK輸入和XOsrc輸出之間的平衡-或變壓器耦合的東西嗎?

(2)如果是這樣,你能否建議我如何配置XO的輸出到巴倫或變壓器?我想知道只需將地面終端更換為XO的輸出就足夠了.

(3)似乎AD9269接受高達480MHz的CLK頻率,內部頻率分頻器提供最終采樣頻率.在ADC性能方面(ENOB,......),哪種時鐘源配置更好?

-高頻時鐘源和高N分頻(例如480MHzclksrc+/6div=80MHz晶振采樣頻率)

-低頻時鐘源且無分頻(例如80MHzclksrc+/1div=80MHz采樣頻率)

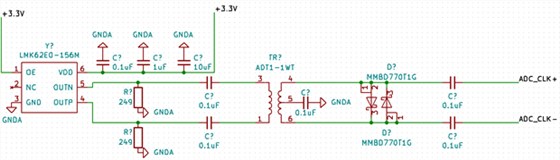

我找到了一個參考設計,它似乎使用差分晶體振蕩器作為時鐘源,來自AD9467.我將XO配置為ADCCLK電路如下所示.

你能否檢查一下是否有任何錯誤或任何評論?

康比電子晶振廠家:本著"顧客至上,質量保證,信譽為本,持續改進"的質量方針,以專注為宗旨在,數碼產品等領域中榮獲"中國優質數碼電子晶振供應商的稱號",在國內服務數千家科技企業,和客戶共同見證晶振頻率的穩定一致性將可調電容改為固定電容,幫助客戶降低產品成本.康比電子以全自動檢測設備儀器,嚴格的現代化生產系統,和ISO9000質量管理體系,快捷的售后服務為您提供優質的產品和服務!

TXC晶振,貼片晶振,7M晶振

TXC晶振,貼片晶振,7M晶振 TXC晶振,貼片晶振,7S晶振

TXC晶振,貼片晶振,7S晶振 TXC晶振,貼片晶振,7A晶振

TXC晶振,貼片晶振,7A晶振 微晶晶振,32.768K晶振,CM9V-T1A壓電石英晶體

微晶晶振,32.768K晶振,CM9V-T1A壓電石英晶體