雖然振蕩器是大多數(shù)電子器件中的關鍵元件,但設計人員在大多數(shù)情況下無需自行設計振蕩器,因為該器件包含大量振蕩器電路.相反,他們只需選擇振蕩器功能所需的晶體和外部電容.如果選擇了錯誤的晶振或外部電容,可能會導致器件無法正常工作,過早失效或無法在預期的溫度范圍內(nèi)工作.

使用此皮爾斯振蕩器電路,用戶可以在并聯(lián)諧振模式下測試和驗證晶體的基本操作.它允許用戶計算和設置關鍵外部電容值,然后讀取振蕩頻率.

石英晶振具有并聯(lián)和串聯(lián)諧振模式,并且振蕩器電路針對一種模式或另一種模式進行校準,但不是兩者都校準.常見的皮爾斯門振蕩器(圖1)使用并聯(lián)晶振模式.這里,晶體由頻率和負載電容(CL)指定,該電容是晶體需要看到以所需頻率振蕩的電容.鎖相環(huán)(PLL)通常用于從如圖所示的振蕩器電路產(chǎn)生的低頻信號中獲得廉價的高頻時鐘信號,這減輕了極高頻晶體的使用.

1.采用并聯(lián)諧振模式的皮爾斯門振蕩器是最常見的石英晶體振蕩器拓撲結構.任何有用的電路模型都必須考慮柵極和其他寄生電容.

設計人員必須選擇電容CL1和CL2的值,以匹配指定的晶體負載電容(CL).最常見的錯誤是假設并行的CL1和CL2的值等于CL的值,這是不準確的.這是因為大多數(shù)設計人員忽略了逆變器門的內(nèi)部輸入和輸出電容(參見CIN和COUT)以及其他一些寄生電容.與外部電容相比,這些電容的價值很大(CL1和CL2);因此,設計者必須計算值CL1和C.L2使用公式1匹配制造商指定的CL:

[CL1+CIN)(CL2+COUT)/CL1+CIN+CL2+COUT]+CSTRAY=CL(1)

如果未指定CIN和COUT,則假設每個為5pF,CSTRAY為3pF,作為起點經(jīng)驗法則.必須通過改變CL1和CL2的起始值來優(yōu)化振蕩器電路,以使總電容等于晶體制造商晶振廠家規(guī)定的CL.微調(diào)電容器可以代替CL1和/或CL2,以便手動調(diào)節(jié)它們的值.(對于CL1和CL2,請務必使用溫度系數(shù)較低的陶瓷電容器(COG或NP0型),并避免使用Z5U材料制成的電容器.)

這個基本測試電路是皮爾斯門振蕩器,它提供貼片晶振頻率的讀數(shù).有兩個電阻調(diào)整(POT1和POT2)以獲得最佳性能,這是頻率以及晶體和寄生電容的函數(shù).

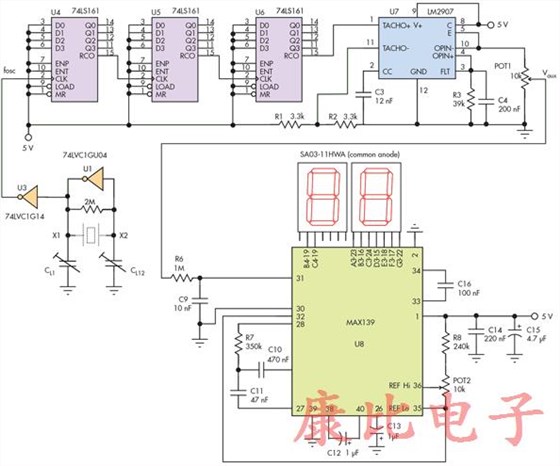

圖2示出了提供連接到端子X1和X2的有源晶振的頻率(以兆赫為單位)的電路的示意圖.該電路使用配置為并聯(lián)諧振(U1)的皮爾斯門振蕩器.它的輸出通過一個無緩沖的反相器(U3),到一系列作為分頻器的四位同步計數(shù)器(U4,U5,U6),再到一個頻率-電壓轉(zhuǎn)換器(U7),以產(chǎn)生一個電壓與振蕩器產(chǎn)生的信號頻率成正比.該電壓由具有內(nèi)部七段驅(qū)動器(U8)的31/2位模數(shù)轉(zhuǎn)換器數(shù)字化,通過兩位LED讀數(shù)顯示晶體頻率.

用戶需要先對電路進行兩次調(diào)整才能使用:

•調(diào)節(jié)電位器POT2以獲得VREF=VREFHi-VREFLo=0.1V.

•對于fOSC=αMHz的晶體,調(diào)整電位器POT1以獲得略高于10αmV的電壓VAUX.因此,對于fOSC=4MHz的晶體,電壓VAUX必須約為42mV.

在進行調(diào)整之后,使用等式1計算電容器CL1和CL2的值以測量晶振的頻率;假設CIN和COUT各自等于7pF,CSTRAY約為3pF,CL1=CL2.

此文件類型包括高分辨率圖形和原理圖(如果適用).

Cesinel公司設計工程師JoseB.Castro-Miguens負責電力電子,儀表工程,信號處理和電力控制,獲得了西班牙馬德里UPCO大學的電氣和電子工程學位.可以通過cmiguens@uvigo.es與他聯(lián)系.

西班牙維哥大學電子系副教授CarlosCastro-Miguens獲得了維哥大學的電子工程學位.他的主要研究興趣是電力電子學(電力轉(zhuǎn)換器的動態(tài)建模和控制,電力轉(zhuǎn)換器的磁性元件設計)和嵌入式系統(tǒng)的設計.

TXC晶振,貼片晶振,7M晶振

TXC晶振,貼片晶振,7M晶振 TXC晶振,貼片晶振,7S晶振

TXC晶振,貼片晶振,7S晶振 TXC晶振,貼片晶振,7A晶振

TXC晶振,貼片晶振,7A晶振 微晶晶振,32.768K晶振,CM9V-T1A壓電石英晶體

微晶晶振,32.768K晶振,CM9V-T1A壓電石英晶體